Automatische Generierung von Schaltplänen für integrierte Standard-Schaltungen

Förderung: BMBF

Ziel

Bereitstellen eines durchgängigen Entwurfsflusses für analoge Schaltungen auf höherer Abstraktionsebene

Herausforderungen

- Erweiterung des Schematic-Driven-Layout Entwurfsflusses mit Schaltplan Generatoren

- Entwicklung eines Tools zur Erstellung von Schaltplan Generatoren

- Methodische Einbindung von Design- Erfahrungen

Konzept

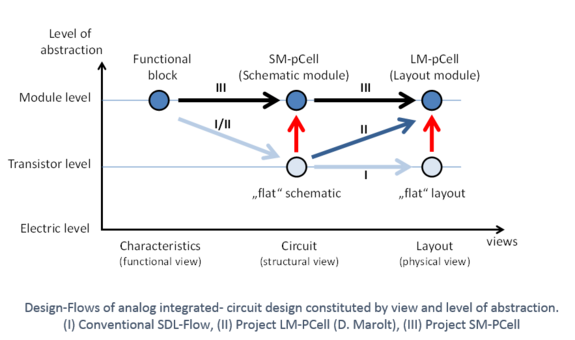

Funktional betrachtet ein Designer die zu entwerfende Schaltung grundsätzlich auf Modulebene (funktionale Sicht, im Bild links). Beim konventionellen sog. Schematic-Driven-Layout (SDL) Design-Flow werden anschließend Schaltung (Circuit) und Layout aber auf der darunter liegenden Transistorebene bearbeitet (im Bild: Flow I). Bereits bestehende Ansätze von Layout-Modul PCells heben die Abstraktionsebene bei der Layouterstellung - im Gegensatz zu einem flachen Layout auf Transistorebene - auf die Modulebene (im Bild rechts). Dies verbessert zwar die Produktivität im Layoutentwurf. Allerdings entsteht dadurch ein Flow, bei dem zweimal zwischen den Hierarchiestufen gewechselt wird (im Bild: Flow II), was im Gesamtablauf des Entwurfsprozesses wiederum erhebliche Informations- und Effizienzverluste zur Folge hat.

Hier setzt unser Vorhaben an: Mit der Einführung von Schematic-Modul PCells wird ein durchgängiger und damit effizienter Entwurfsfluss auf Modulebene ohne Informationsverlust erreicht (im Bild: Flow III). Im Ergebnis resultiert hieraus eine signifikante Verbesserung von Qualität und Produktivität beim analogen IC-Design.

Beispiel

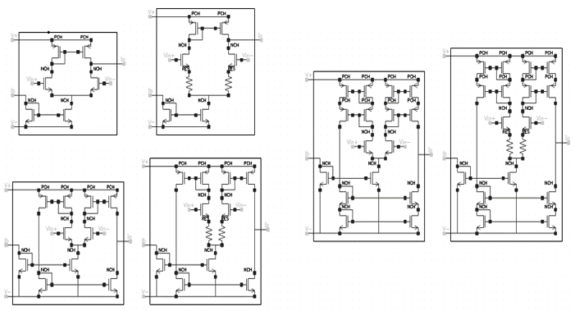

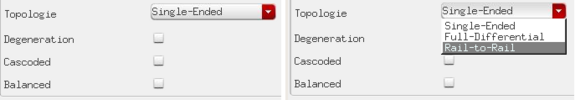

Im hier gezeigten Beispiel ist eine Schematic-Modul PCell als OTA-Schaltungsvariante ausgeführt. Die OTA-PCell wurde mit Hilfe des am E&D entwickelten Tools "PCDS" entworfen. Alle Screenshots wurden mit ein und derselben Schematic-Module PCell erstellt. In Bild 1 erkennen wir eine einfache OTA-Struktur wie sie in vielen Lehrbüchern zu finden ist. In Bild 2 wurde die Struktur durch eine so genannte Source- Degeneration ergänzt. Bild 3 und 4 stellen differentielle Varianten der Abbildungen 1 und 2 dar. In Bild 5 und 6 erkennen wir die Strukturen aus Bild 3 und 4 mit kaskodierten Stromspiegeln.

Der Wechsel zwischen den einzelnen Strukturen erfolgt über das Eigenschafts-Menü der PCell und ist mit Hilfe eines Klicks möglich.

- Kontakt und Ansprechpartner

Prof. Dr.-Ing. Jürgen Scheible

Gebäude E&D

Raum R1-102

Tel. +49 07121 271-7089

Mail senden »

- Seite drucken

- Seite teilen